# AG32 MCU

## **DATA SHEET**

**Revision:1.0**

## **Features**

|                                               | AG32 MCU     |              |              |                       |              |  |  |  |  |  |  |  |  |

|-----------------------------------------------|--------------|--------------|--------------|-----------------------|--------------|--|--|--|--|--|--|--|--|

| AGM Device                                    | AG32VF103    | AG32VF107    | AG32VF205    | G32VF205 AG32VF303 AG |              |  |  |  |  |  |  |  |  |

| Max Speed (MHz)                               | 168          | 168          | 184          | 208                   | 248          |  |  |  |  |  |  |  |  |

| SRAM                                          | 128K         | 128K         | 128K         | 128K                  | 128K         |  |  |  |  |  |  |  |  |

| Flash                                         | 256K         | 1M           | 1M           | 1M                    | 1M           |  |  |  |  |  |  |  |  |

| CAN2.0                                        | 1            | 1            | 1            | 1                     | 1            |  |  |  |  |  |  |  |  |

| UART                                          | 5            | 5            | 5            | 5                     | 5            |  |  |  |  |  |  |  |  |

| I2C                                           | 2            | 2            | 2            | 2                     | 2            |  |  |  |  |  |  |  |  |

| Basic Timer                                   | 2            | 2            | 2            | 2                     | 2            |  |  |  |  |  |  |  |  |

| Advanced Timer                                | 5            | 5            | 5            | 5                     | 5            |  |  |  |  |  |  |  |  |

| Support SDIO,Ethernet<br>MAC                  | 1            | √            |              | /                     | $\checkmark$ |  |  |  |  |  |  |  |  |

| Support USB FS+OTG                            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$          | $\checkmark$ |  |  |  |  |  |  |  |  |

| Watchdog                                      | V            | V            | $\checkmark$ | $\checkmark$          | $\checkmark$ |  |  |  |  |  |  |  |  |

| 3 x 12 bit,1M SPS ADCs(17<br>channels),2 DACs | V            | $\checkmark$ | $\checkmark$ | $\checkmark$          |              |  |  |  |  |  |  |  |  |

| 2 x Comparator                                | V            | $\checkmark$ | $\checkmark$ | $\checkmark$          | $\checkmark$ |  |  |  |  |  |  |  |  |

| RTC                                           | V            | $\checkmark$ | $\checkmark$ | $\checkmark$          | $\checkmark$ |  |  |  |  |  |  |  |  |

| SPI                                           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$          | $\checkmark$ |  |  |  |  |  |  |  |  |

## <u>contents</u>

| 1 Description                                                        | 7  |

|----------------------------------------------------------------------|----|

| 1.1 Chip architecture                                                | 7  |

| 1.2 Power control                                                    | 8  |

| 1.2.1 Power supplies                                                 |    |

| 1.2.2 Independent ADC and DAC converter supply and reference voltage | 9  |

| 1.2.3 Battery backup domain                                          | 9  |

| 1.2.4 Voltage regulator                                              |    |

| 1.2.5 Power on reset (POR)/power down reset (PDR)                    | 10 |

| 1.2.6 Low-power modes                                                | 10 |

| 1.2.6.1 Slowing down system clocks                                   | 11 |

| 1.2.6.2 Peripheral clock gating                                      | 11 |

| 1.2.6.3 Sleep mode                                                   | 11 |

| 1.2.6.4 Stop mode                                                    | 13 |

| 1.2.6.5 Standby mode                                                 | 14 |

| 1.2.6.6 Auto-wakeup (AWU) from low-power mode                        | 15 |

| 1.2.7 Power control registers                                        | 16 |

| 1.2.7.1 Power control register (PWR_CR)                              | 16 |

| 1.2.7.2 Power control/status register (PWR_CSR)                      | 17 |

| 1.3 Backup registers (BKP)                                           | 18 |

| 1.3.1 BKP introduction                                               | 18 |

| 1.3.2 BKP main features                                              |    |

| 1.3.3 RTC calibration                                                |    |

| 1.3.4 BKP registers                                                  | 18 |

| 1.3.4.1 Backup data register x (BKP_DRx) (x = 117)                   | 18 |

| 1.3.4.2 RTC clock calibration register (BKP_RTCCR)                   | 19 |

| 1.4 Reset and clock control                                          | 21 |

| 1.4.1 Reset                                                          | 21 |

| 1.4.1.1 System reset                                                 | 21 |

| 1.4.1.2 Power reset                                                  | 22 |

| 1.4.1.3 Backup domain reset                                          | 22 |

| 1.4.2 Clocks                                                         | 22 |

| 1.4.2.1 HSE clock                                                    | 24 |

| 1.4.2.2 HSI clock                                                    | 25 |

| 1.4.2.3 PLL                                                          | 25 |

| 1.4.2.4 LSE clock                                                    | 25 |

| 1.4.2.5 LSI clock                                                    | 25 |

| 1.4.2.6 System clock (SYSCLK) selection                              | 26 |

| 1.4.2.7 RTC clock                                                    | 26 |

| 1.4.2.8 Watchdog clock                                               | 26 |

| 1.4.3 Reset and clock control registers                              | 27 |

| 1.4.3.1 Clock control register (RCC_CR)                     | 27 |

|-------------------------------------------------------------|----|

| 1.4.3.2 Clock configuration register (RCC_CFGR)             |    |

| 1.4.3.3 Clock interrupt register (RCC_CIR)                  |    |

| 1.4.3.4 APB2 peripheral reset register (RCC_APB2RSTR)       |    |

| 1.4.3.5 APB1 peripheral reset register (RCC_APB1RSTR)       |    |

| 1.4.3.6 AHB peripheral clock enable register (RCC_AHBENR)   |    |

| 1.4.3.7 APB2 peripheral clock enable register (RCC_APB2ENR) |    |

| 1.4.3.8 APB1 peripheral clock enable register (RCC_APB1ENR) |    |

| 1.4.3.9 Backup domain control register (RCC_BDCR)           |    |

| 1.4.3.10 Control/status register (RCC_CSR)                  |    |

| 1.5 Analog-to-digital converter (ADC)                       | 31 |

| 1.5.1 ADC introduction                                      |    |

| 1.5.2 Characteristics                                       |    |

| 1.5.3 Pins and internal signals                             |    |

|                                                             | 33 |

| 1.5.5 ADC output data                                       |    |

| 1.5.6 Analog watchdog                                       |    |

| 1.5.7 Temperature sensor                                    |    |

| 1.6 Digital-to-analog converter (DAC)                       | 35 |

| 1.6.1 Overview                                              |    |

| 1.6.2 DAC main features                                     |    |

| 1.6.3 DAC output buffer enable                              |    |

| 1.6.4 DAC output voltage                                    |    |

| 1.7 Comparator (CMP)                                        | 37 |

| 1.7.1 Overview                                              |    |

| 1.7.2 Characteristic                                        |    |

| 1.8 Real-time clock (RTC)                                   | 39 |

| 1.8.1 RTC introduction                                      | 39 |

| 1.8.2 RTC main features                                     |    |

| 1.8.3 RTC functional description                            | 40 |

| 1.8.4 RTC registers                                         | 44 |

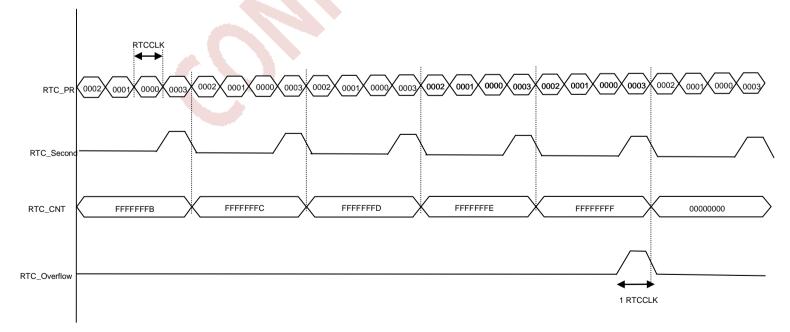

| 1.9 Independent watchdog (IWDG)                             | 49 |

| 1.9.1 IWDG main features                                    |    |

| 1.9.2 IWDG functional description                           | 49 |

| 1.9.3 Debug mode                                            | 50 |

| 1.9.4 IWDG registers                                        | 50 |

| 1.10 FPGA core                                              | 52 |

| 1.10.1 I/O                                                  |    |

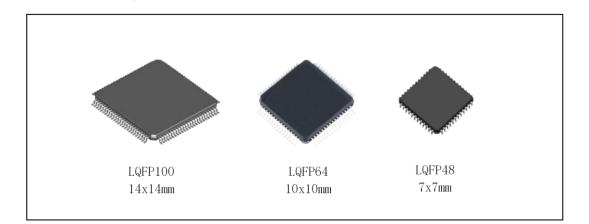

| 2 Package                                                   | 54 |

| 3 Pin definitions                                           | 56 |

| 4 Memorymapping                                             | 60 |

| 5 Electricalcharacteristics                         | 61 |

|-----------------------------------------------------|----|

| 5.1 Absolute maximum ratings                        | 61 |

| 5.2 Recommended DC characteristics                  | 61 |

| 5.3 Power consumption                               | 62 |

| 5.4 Power up/down                                   |    |

| 5.5 External clock characteristics                  |    |

| 5.6 Internal clock source characteristics           |    |

| 5.7 PLL characteristics                             |    |

| 5.8 emory characteristics                           |    |

| 5.9 IO characteristics                              |    |

|                                                     |    |

|                                                     | 67 |

|                                                     | 67 |

| 5.12 Comparator characteristics                     |    |

| 5.13 I <sup>2</sup> C characteristics               | 68 |

| 5.14 SPI characteristics                            | 69 |

| 5.15 NRST pin characteristics                       | 70 |

| 5.16 USART characteristics                          | 72 |

| 5.17 SDIO characteristics                           | 72 |

| 5.18 USB characteristics                            | 73 |

| 5.19 TIMER characteristics                          | 74 |

| 5.20 CRC(Cyclic redundancy check calculation unit ) | 74 |

| 5.20.1 Introduction                                 | 74 |

| 5.20.2 CRC main features                            | 75 |

| 5.20.3 CRC functional description                   | 75 |

| 5.20.3.1 CRC block diagram                          | 75 |

| 5.20.3.2 CRC internal signals                       | 76 |

| 5.20.3.3 CRC operation                              | 76 |

| 5.20.4 CRC registers                                |    |

| 5.20.4.1 Data register (CRC_DR)                     |    |

| 5.20.4.2 Independent data register (CRC_IDR)        |    |

| 5.20.4.3 Control register (CRC_CR)                  |    |

| 5.20.4.4 Initial CRC value (CRC_INIT)               |    |

| 5.20.4.5 CRC polynomial (CRC_POL)                   |    |

| 5.20.4.6 CRC register map                           |    |

| 5.21 DMA-Summary of registers                       |    |

| 5.22 Interrupt Controller                           | 85 |

| 5.22.1 Interrupt overview                                                                 | 85   |

|-------------------------------------------------------------------------------------------|------|

| 5.22.1.1 Local interrupts                                                                 |      |

| 5.22.1.2 External interrupts                                                              |      |

| 5.22.1.3 Machine software interrupt                                                       |      |

| 5.22.1.4 Machine timer interrupt                                                          | 87   |

| 5.22.1.5 Overall priority                                                                 | 87   |

| 5.22.1.6 Interrupt enable                                                                 | 88   |

| 5.22.2 Interrupt registers                                                                | 88   |

| 5.23 Timer-Summary of registers                                                           | 90   |

| 5.24 UART-Summary of registers                                                            | 91   |

| 5.25 WatchDog-Summary of registers                                                        | 92   |

| 5.26 flash-SPIcontrol                                                                     | 93   |

| 5.26.1 Overview                                                                           | 93   |

| 5.26.1.1 Characteristics of this spi controller                                           | _ 93 |

| 5.26.1.2 the concept of PHASE                                                             | 93   |

| 5.26.1.3 Module block diagram                                                             | 94   |

| 5.26.1.4 Top port                                                                         | _ 96 |

| 5.26.2 Instructions for use of the module                                                 | _ 97 |

| 5.26.2.1 System integration method                                                        | _ 97 |

| 5.26.2.2 register description                                                             |      |

| 5.26.2.2.1 SPCR register (address: BASE_ADDR+8'h00)                                       | _ 98 |

| 5.26.2.2.2 phase _ ctrl0 ~ phase _ ctrl7 registers (address: base _ addr+8' h10 ~ 8' h2c) | 100  |

| 5.26.2.2.3 phase _ data0 ~ phase _ data7 registers (address: base _ addr+8' h30 ~ 8' h40  | -    |

| 5.26.2.3 description of PHASE_ACTION                                                      |      |

| 5.26.2.3.1 TX                                                                             |      |

| 5.26.2.3.2 DUMMY TX                                                                       |      |

| 5.26.2.3.3 RX                                                                             | 103  |

| 5.26.2.3.4 POLL                                                                           | 103  |

| 5.26.2.3.5 Pay attention.                                                                 |      |

| 5.26.2.4 Software configuration sequence                                                  |      |

| 5.26.2.5 Example of software configuration                                                |      |

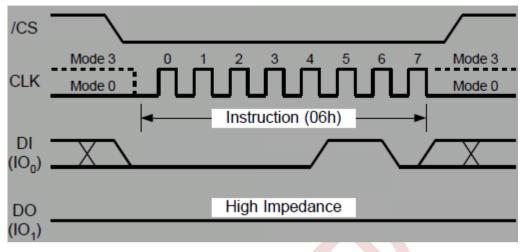

| 5.26.2.5.1 Send the Write Enable(06h) command.                                            | -    |

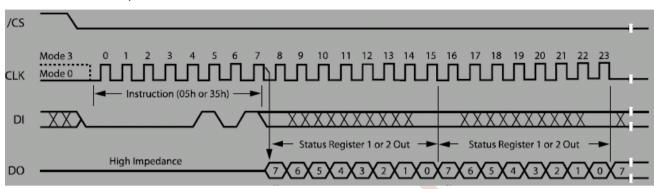

| 5.26.2.5.2 Send the Read Status Register-1(05h) command.                                  |      |

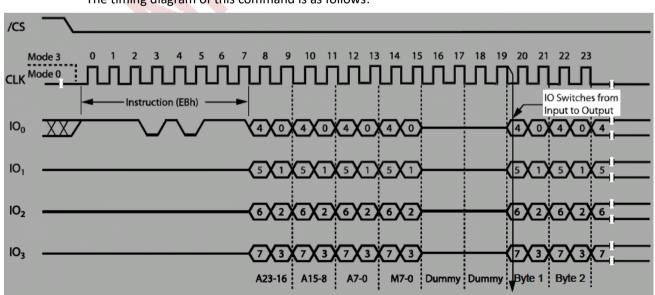

| 5.26.2.5.3 Read data with Fast Read Quad IO(EBh) command                                  | 107  |

## 1 Description

The AG32 family of 32-bit microcontrollers is designed to offer new degrees of freedom and rich compatible peripherals, and compatible pin and features to MCU users. AG32F103 product series offers supreme quality, stability, and exceptional pricing value.

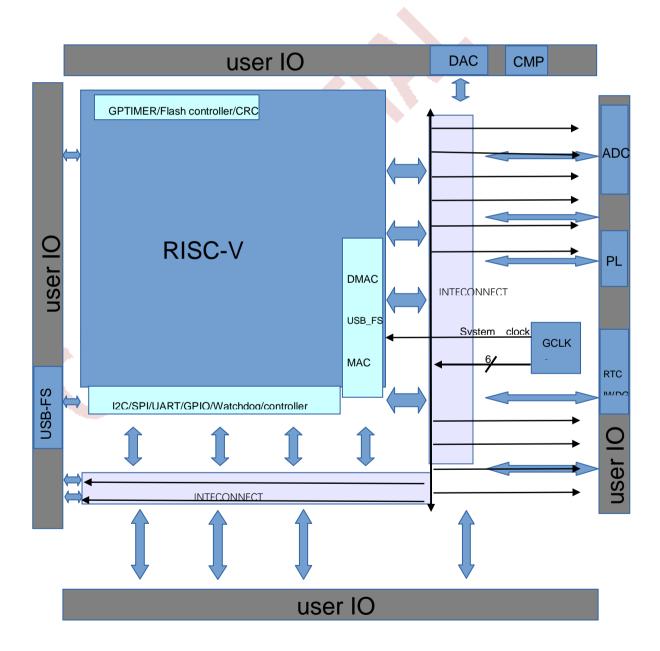

## **1.1** Chip architecture

## **1.2 Power control**

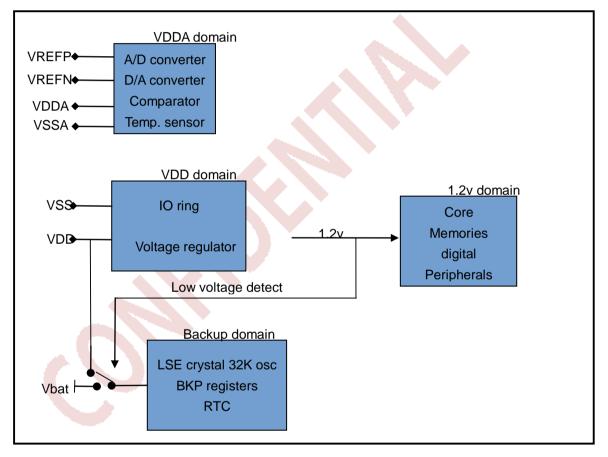

#### **1.2.1** Power supplies

The AGRV2K requires a 3.0-to-3.6 V operating voltage supply (VDD). An embedded regulator is used to supply the internal 1.2V digital power.

The real-time clock (RTC) and backup registers can be powered from the VBAT voltage when the main VDD supply is powered off.

#### Power supply overview

## **1.2.2** Independent ADC and DAC converter supply and reference

#### voltage

To improve conversion accuracy, the ADC and the DAC have an independent power supply which can be separately filtered and shielded from noise on the PCB.

(1) The ADC and DAC voltage supply input is available on a separate VDDA pin.

(2) An isolated supply ground connection is provided on pin VSSA.

When available (according to package), VREFN must be tied to VSSA.

To ensure a better accuracy on low-voltage inputs and outputs, the user can connect a separate external reference voltage on VREFP. VREFP is the highest voltage, represented by the full scale value, for an analog input (ADC) or output (DAC) signal. The voltage on VREFP can range from 3.0V to VDDA.

#### **1.2.3** Battery backup domain

To retain the content of the Backup registers and supply the RTC function when VDD is turned off, VBAT pin can be connected to an optional standby voltage supplied by a battery or by another source.

The VBAT pin powers the RTC unit, the LSE oscillator and the PA5\_RTC, OSC32\_IN and OSC32\_OUT Pins, allowing the RTC to operate even when the main digital supply (VDD) is turned off.

If no external battery is used in the application, it is recommended to connect VBAT externally to VDD with a 100nF external ceramic decoupling capacitor.

When the backup domain is supplied by VDD (analog switch connected to VDD), the following functions are available:

(1) OSC32\_IN and OSC32\_OUT can be used as LSE pins only.

(2) PA5\_RTC can be used as GPIO, RTC Calibration Clock, RTC Alarm or second output.

When the backup domain is supplied by VBAT (analog switch connected to VBAT because VDD is not present), the following functions are available:

(1) OSC32\_IN and OSC32\_OUT can be used as LSE pins only.

(2) PA5\_RTC can be used as RTC Alarm or Second output.

#### 1.2.4 Voltage regulator

The voltage regulator is always enabled after Reset. It works in two different modes depending on the application modes.

(1) In Run and Stop modes, the regulator supplies full power to the 1.2V domain (core, memories,

digital peripherals and fpga core logic).

(2) In Standby Mode, the regulator is powered off. The contents of the registers and SRAM are lost except for the Standby circuitry and the Backup Domain.

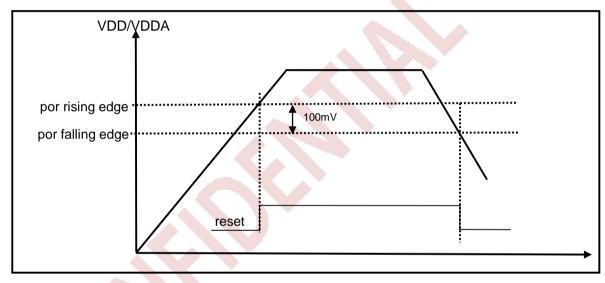

## **1.2.5** Power on reset (POR)/power down reset (PDR)

The device has an integrated POR/PDR circuitry that allows proper operation starting from/down to 2.2V. The device remains in Reset mode when VDD/VDDA is below a specified threshold, VPOR/PDR, without the need for an external reset circuit.

Power on reset/power down reset waveform

## 1.2.6 Low-power modes

By default, the micro-controller is in Run mode after a system or a power Reset. Several low-power modes are available to save power when the CPU does not need to be kept running. It is up to the user to select the mode that gives the best compromise between low-power consumption, short startup time and available wakeup sources.

The AGRV2K devices feature three low-power modes:

(1) Sleep mode (CPU clock off, all peripherals including MCU core peripherals are kept running)

(2) Stop mode (all clocks are stopped)

(3) Standby mode (1.2V domain powered-off)

In addition, the power consumption in Run mode can be reduce by one of the following means:

(1) Slowing down the system clocks.

(2) Gating the clocks to the APB and AHB peripherals when they are unused.

| Table 1. Low-power mode summary  |                                                                |                                                                                         |                                     |                             |                      |  |  |  |

|----------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------|-----------------------------|----------------------|--|--|--|

| Mode name                        | Entry                                                          | Wakeup                                                                                  | Effect on 1.2V domain clocks        | Effect on VDD domain clocks | Voltage<br>regulator |  |  |  |

| Sleep                            | WFI                                                            | Any interrupt                                                                           | CPU clock OFF<br>no effect on other |                             |                      |  |  |  |

| (Sleep now or<br>Sleep-on -exit) | WFE                                                            | Wakeup event                                                                            | clocks or analog<br>clock sources   | None                        | ON                   |  |  |  |

| Stop                             | PDDS and<br>LPDS<br>bits +<br>SLEEPDEEP<br>bit + WFI or<br>WFE | Any EXTI line<br>(configured in the<br>EXTI registers)                                  | All 1.2V domain<br>clocks OFF       | HSI and HSE                 | ON                   |  |  |  |

| Standby                          | PDDS bit +<br>SLEEPDEEP<br>bit +<br>WFI or WFE                 | bit + WFI or<br>WFEWKUP pin rising<br>edge, RTC alarm,<br>external reset in<br>NRST pin |                                     | oscillators OFF             | OFF                  |  |  |  |

#### Table 1. Low-power mode summary

#### 1.2.6.1 Slowing down system clocks

In Run mode the speed of the system clocks can be reduced. And also slow down peripherals before entering Sleep mode.

#### 1.2.6.2 Peripheral clock gating

In Run mode, the clocks for individual peripherals and memories can be stopped at any time to reduce power consumption.

To further reduce power consumption in Sleep mode the peripheral clocks can be disabled prior to executing the WFI or WFE instructions.

#### 1.2.6.3 Sleep mode

Entering Sleep mode

The Sleep mode is entered by executing the WFI (Wait For Interrupt) or WFE (Wait for Event) instructions. Two options are available to select the Sleep mode entry mechanism, depending on the SLEEPONEXIT bit in the System Control register:

(1) Sleep-now: if the SLEEPONEXIT bit is cleared, the MCU enters Sleep mode as soon as WFI or

WFE instruction is executed.

(2) Sleep-on-exit: if the SLEEPONEXIT bit is set, the MCU enters Sleep mode as soon as it exits the lowest priority ISR.

In the Sleep mode, all I/O pins keep the same state as in the Run mode.

Exiting Sleep mode

If the WFI instruction is used to enter Sleep mode, any peripheral interrupt acknowledged by the nested vectored interrupt controller (NVIC) can wake up the device from Sleep mode. If the WFE instruction is used to enter Sleep mode, the MCU exits Sleep mode as soon as an event occurs. The wakeup event can be generated either by:

(1) enabling an interrupt in the peripheral control register but not in the NVIC, and enabling the SEVONPEND bit in the System Control register. When the MCU resumes from WFE, the peripheral interrupt pending bit and the peripheral NVIC IRQ channel pending bit (in the NVIC interrupt clear pending register) have to be cleared.

(2) or configuring an external or internal EXTI line in event mode. When the CPU resumes from WFE, it is not necessary to clear the peripheral interrupt pending bit or the NVIC IRQ channel pending bit as the pending bit corresponding to the event line is not set. This mode offers the lowest wakeup time as no time is wasted in interrupt entry/exit.

| Sleep-now mode | Description                                                                                                                                                                    |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode entry     | <ul> <li>WFI (Wait for Interrupt) or WFE (Wait for Event) while:</li> <li>SLEEPDEEP = 0 and</li> <li>SLEEPONEXIT = 0</li> <li>Refer to the System Control register.</li> </ul> |

| Mode exit      | If WFI was used for entry:<br>Interrupt: Refer to : Interrupt and exception vectors<br>If WFE was used for entry<br>Wakeup event: Refer to : Wakeup event management           |

| Wakeup latency | None                                                                                                                                                                           |

#### Table 2. Sleep-now

| Table 3. Sleep-on-exit | . Sleep-on-exit | able 3. | Т |

|------------------------|-----------------|---------|---|

|------------------------|-----------------|---------|---|

| Sleep-on-exit  | Description                                                                                                          |

|----------------|----------------------------------------------------------------------------------------------------------------------|

| Mode entry     | WFI (wait for interrupt) while:<br>- SLEEPDEEP = 0 and<br>- SLEEPONEXIT = 1<br>Refer to the System Control register. |

| Mode exit      | Interrupt: refer to: Interrupt and exception vectors.                                                                |

| Wakeup latency | None                                                                                                                 |

#### **1.2.6.4** Stop mode

The Stop mode is based on the MCU deep-sleep mode combined with peripheral clock gating. In Stop mode, all clocks in the 1.2V domain are stopped, the PLL, the HSI and the HSE oscillators are disabled. SRAM and register contents are preserved.

In the Stop mode, all I/O pins keep the same state as in the Run mode.

#### Entering Stop mode

Refer to Table 4 for details on how to enter the Stop mode.

If Flash memory programming is ongoing, the Stop mode entry is delayed until the memory access is finished.

If an access to the APB domain is ongoing, The Stop mode entry is delayed until the APB access is finished.

In Stop mode, the following features can be selected by programming individual control bits:

(1) Independent watchdog (IWDG): the IWDG is started by writing to its enable register or by hardware option. Once started it cannot be stopped except by a Reset.

(2) Real-time clock (RTC): this is configured by the RTCEN bit in the Backup domain control register (RCC\_BDCR).

(3) External 32.768 kHz oscillator (LSE OSC): this is configured by the LSEON bit in the Backup domain control register (RCC\_BDCR).

The ADC or DAC can also consume power during the Stop mode, unless they are disabled before entering it.

#### Exiting Stop mode

Refer to Table 4 for more details on how to exit Stop mode.

When exiting Stop mode by issuing an interrupt or a wakeup event, the HSI RC oscillator is selected as system clock.

|                | Table 4. Stop mode                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stop mode      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Mode entry     | <ul> <li>WFI (Wait for Interrupt) or WFE (Wait for Event) while:</li> <li>Set SLEEPDEEP bit in System Control register</li> <li>Clear PDDS bit in Power Control register (PWR_CR)</li> <li>Note: To enter Stop mode, all EXTI Line pending bits (in Pending register (EXTI_PR)), all peripheral interrupt pending bits, and RTC Alarm flag must be reset. Otherwise, the Stop mode entry procedure is ignored and program execution continues.</li> </ul> |

| Mode exit      | If WFI was used for entry:<br>Any EXTI Line configured in Interrupt mode (the corresponding EXTI<br>Interrupt vector must be enabled in the NVIC). Refer to:<br>Interrupt and exception vectors.<br>If WFE was used for entry:<br>Any EXTI Line configured in event mode. Refer to:<br>Wakeup event management                                                                                                                                            |

| Wakeup latency | HSI RC wakeup time                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### 1.2.6.5 Standby mode

The Standby mode allows to achieve the lowest power consumption. It is based on the deep-sleep mode, with the voltage regulator disabled. The 1.2V domain is consequently powered off. The PLL, the HSI oscillator and the HSE oscillator are also switched off. SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

#### **Entering Standby mode**

Refer to Table 5 for more details on how to enter Standby mode.

In Standby mode, the following features can be selected by programming individual control bits:

(1) Independent watchdog (IWDG): the IWDG is started by writing to its enable register or by hardware option. Once started it cannot be stopped except by a reset.

(2) Real-time clock (RTC): this is configured by the RTCEN bit in the Backup domain control register (RCC\_BDCR).

(3) External 32.768 kHz oscillator (LSE OSC): this is configured by the LSEON bit in the Backup domain control register (RCC\_BDCR)

#### **Exiting Standby mode**

The micro-controller exits the Standby mode when an external reset (NRST pin), an IWDG reset, a

rising edge or falling edge on the WKUP pin or the rising edge of an RTC alarm occurs. All registers are reset after wakeup from Standby.

After waking up from Standby mode, program execution restarts in the same way as after a Reset. The SBF status flag in the Power control/status register (PWR\_CSR) indicates that the MCU was in Standby mode.

Refer to Table 5 for more details on how to exit Standby mode.

| Stop mode      | Description                                                                                                                                                                                                                                                                                                                    |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode entry     | <ul> <li>WFI (Wait for Interrupt) or WFE (Wait for Event) while:</li> <li>– Set SLEEPDEEP in System Control register</li> <li>– Set PDDS bit in Power Control register (PWR_CR)</li> <li>– Clear WUF bit in Power Control/Status register (PWR_CSR)</li> <li>– No interrupt (for WFI) or event (for WFI) is pending</li> </ul> |

| Mode exit      | WKUP pin rising edge, RTC alarm event's rising edge, external Reset in NRST pin, IWDG Reset.                                                                                                                                                                                                                                   |

| Wakeup latency | Reset phase                                                                                                                                                                                                                                                                                                                    |

#### Table 5. Standby mode

I/O states in Standby mode

In Standby mode, all I/O pins are high impedance except:

- (1) Reset pin (still available)

- (2) CLKRTCOUT pin if configured for calibration out

(3) WKUP pin, if enabled

#### 1.2.6.6 Auto-wakeup (AWU) from low-power mode

The RTC can be used to wakeup the MCU from low-power mode without depending on an external interrupt (Auto-wakeup mode). The RTC provides a programmable time base for waking up from Stop or Standby mode at regular intervals. For this purpose, two of the three alternative RTC clock sources can be selected by programming the RTCSEL[1:0] bits in the Backup domain control register (RCC\_BDCR):

(1) Low-power 32.768 kHz external crystal oscillator (LSE OSC).

This clock source provides a precise time base with very low-power consumption.

(2) Low-power internal RC Oscillator (LSI RC)

This clock source has the advantage of saving the cost of the 32.768 kHz crystal.

## **1.2.7** Power control registers

#### 1.2.7.1 Power control register (PWR\_CR)

Address offset: 0x00

Reset value: 0x0000 0000 (reset by wakeup from Standby mode)

| 31   30   29   28   27   26   25   24   23   22   21   20   19   18   1 |          |  |  |  |  |  |  |  |  | 17 | 16 |  |

|-------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|--|----|----|--|

|                                                                         | reserved |  |  |  |  |  |  |  |  |    |    |  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7 | 6     | 5    | 4 | 3     | 2     | 1    | 0    |

|----|----|----|----|----|----|---|-----|---|-------|------|---|-------|-------|------|------|

|    |    |    |    |    |    |   | DBP |   | rese  | rved |   | CSBF  | CWUF  | PDDS | LPDS |

|    |    |    |    |    |    |   | rw  |   | icse. | Iveu |   | rc_w1 | rc_w1 | rw   | rw   |

Bit 8 DBP: Disable backup domain write protection.

In reset state, the RTC and backup registers are protected against parasitic write access. This bit

must be set to enable write access to these registers.

0: Access to RTC and Backup registers disabled

1: Access to RTC and Backup registers enabled

Bit 3 CSBF: Clear standby flag.

This bit is always read as 0.

0: No effect

1: Clear the SBF Standby Flag (write).

Bit 2 CWUF: Clear wakeup flag.

This bit is always read as 0.

0: No effect

1: Clear the WUF Wakeup Flag after 2 System clock cycles. (write)

Bit 1 PDDS: Power down deep-sleep.

This bit is set and cleared by software. It works together with the LPDS bit.

0: Enter Stop mode when the CPU enters Deep-sleep. The regulator status depends on the LPDS bit.

1: Enter Standby mode when the CPU enters Deep-sleep.

Bit 0 LPDS: Low-power deep-sleep.

This bit is set and cleared by software. It works together with the PDDS bit.

0: Voltage regulator on during Stop mode

1: Voltage regulator in low-power mode during Stop mode

## 1.2.7.2 Power control/status register (PWR\_CSR)

#### Address offset: 0x04

#### Reset value: 0x0000 0000 (not reset by wakeup from Standby mode)

Additional APB cycles are needed to read this register versus a standard APB read.

| 31      | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| reserve | ed |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 15       | 14   | 13 | 12 | 11 | 10 | 9 | 8    | 7        | 6  | 5 | 4 | 3 | 2 | 1   | 0   |

|----------|------|----|----|----|----|---|------|----------|----|---|---|---|---|-----|-----|

| reserve  | ad a |    |    |    |    |   | EWUP | rocorric | d  |   |   |   |   | SBF | WUF |

| 10501 00 | u    |    |    |    |    |   | rw   | reserve  | u. |   |   |   |   | r   | r   |

Bit 8 EWUP: Enable WKUP pin

This bit is set and cleared by software.

0: WKUP pin is used for general purpose I/O. An event on the WKUP pin does not wakeup the device from Standby mode.

1: WKUP pin is used for wakeup from Standby mode and forced in input pull down configuration (rising edge on WKUP pin wakes-up the system from Standby mode).

Note: This bit is reset by a system Reset.

Bit 1 SBF: Standby flag

This bit is set by hardware and cleared only by a POR/PDR (power on reset/power down reset) or by setting the CSBF bit in the Power control register (PWR\_CR)

0: Device has not been in Standby mode

1: Device has been in Standby mode

Bit 0 WUF: Wakeup flag

This bit is set by hardware and cleared by hardware, by a system reset or by setting the CWUF bit in the Power control register (PWR\_CR)

0: No wakeup event occurred

1: A wakeup event was received from the WKUP pin or from the RTC alarm

Note: An additional wakeup event is detected if the WKUP pin is enabled (by setting the EWUP bit) when the WKUP pin level is already high.

## 1.3 Backup registers (BKP)

### **1.3.1** BKP introduction

The backup registers are sixteen two 16-bit registers for storing 32 bytes of user application data. They are implemented in the backup domain that remains powered on by VBAT when the VDD power is switched off. They are not reset when the device wakes up from Standby mode or by a system reset or power reset.

In addition, the BKP control registers are used to manage the RTC calibration.

After reset, access to the Backup registers and RTC is disabled and the Backup domain (BKP) is protected against possible parasitic write access. To enable access to the Backup registers and the RTC, proceed as follows:

(1) enable the power and backup interface clocks by setting the PWREN and BKPEN bits in the RCC\_APB1ENR register

(2) set the DBP bit the Power Control Register (PWR\_CR) to enable access to the Backup registers and RTC.

#### 1.3.2 BKP main features

(1) 32-byte data registers

(2) Calibration register for storing the RTC calibration value

(3) Possibility to output the RTC Calibration Clock, RTC Alarm pulse or Second pulse on pin PC13

#### 1.3.3 **RTC** calibration

For measurement purposes, the RTC clock with a frequency divided by 64 can be output on the PC13 pin. This is enabled by setting the CCO bit in the RTC clock calibration register (BKP\_RTCCR). The clock can be slowed down by up to 121 ppm by configuring CAL[6:0] bits.

#### **1.3.4** BKP registers

#### 1.3.4.1 Backup data register x (BKP\_DRx) (x = 1 ..17)

Address offset:

#### Reset value: 0x0000 0000

| 15     | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| D<15:0 | 0> |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| rw     | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 15:0: D[15:0] Backup data

These bits can be written with user data.

Note: The BKP\_DRx registers are not reset by a System reset or Power reset or when the device

wakes up from Standby mode.

They are reset by a Backup Domain reset.

#### 1.3.4.2 RTC clock calibration register (BKP\_RTCCR)

Address offset:

Reset value: 0x0000 0000

| 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8    | 7   | 6      | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|------|------|-----|--------|----|----|----|----|----|----|

|    |    |    |    |    |    | ASOS | ASOE | C00 | CAL<6: | 0> |    |    |    | 1  |    |

|    |    |    |    |    |    | rw   | rw   | rw  | rw     | rw | rw | rw | rw | rw | rw |

Bit 9 ASOS: Alarm or second output selection

When the ASOE bit is set, the ASOS bit can be used to select whether the signal output on the PC13 pin is the RTC Second pulse signal or the Alarm pulse signal:

0: RTC Alarm pulse output selected

1: RTC Second pulse output selected

Note: This bit is reset only by a Backup domain reset.

Bit 8 ASOE: Alarm or second output enable

Setting this bit outputs either the RTC Alarm pulse signal or the Second pulse signal on the PC13 pin depending on the ASOS bit.

0: output disable

1: output enable

The output pulse duration is one RTC clock period. The PC13 pin must not be enabled while the ASOE bit is set.

Note: This bit is reset only by a Backup domain reset.

Bit 7 CCO: Calibration clock output

0: No effect

1: Setting this bit outputs the RTC clock with a frequency divided by 64 on the PC13 pin.

Note: This bit is reset when the VDD supply is powered off.

Bit 6:0 CAL[6:0]: Calibration value

This value indicates the number of clock pulses that will be ignored every 2^20 clock pulses. This allows the calibration of the RTC, slowing down the clock by steps of 1000000/2^20PPM. The clock of the RTC can be slowed down from 0 to 121PPM.

## 1.4 Reset and clock control

#### 1.4.1 Reset

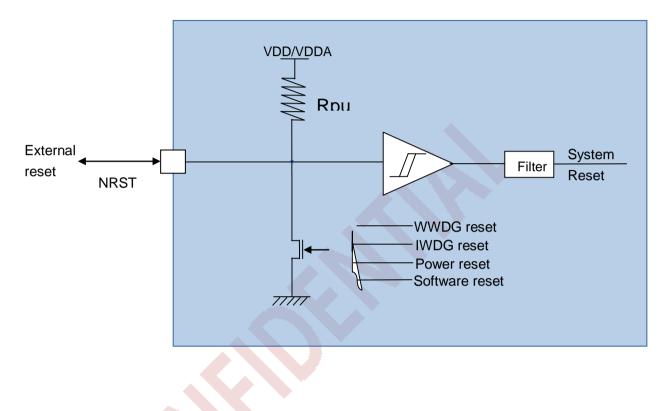

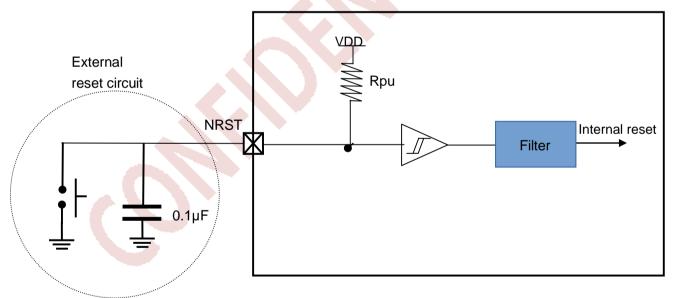

There are three types of reset: system reset, power reset and backup domain reset.

#### 1.4.1.1 System reset

A system reset sets all registers to their reset values except the reset flags in the clock controller CSR register and the registers in the Backup domain.

A system reset is generated when one of the following events occurs:

(1) A low level on the NRST pin (external reset)

- (2) Window watchdog end of count condition (WWDG reset)

- (3) Independent watchdog end of count condition (IWDG reset)

- (4) A software reset (SW reset)

- (5) Low-power management reset

The reset source can be identified by checking the reset flags in the Control/Status register, RCC\_CSR.

#### Software reset

The SYSRESETREQ bit in MCU Application Interrupt and Reset Control Register must be set to force a software reset on the device.

#### Low-power management reset

There are two ways to generate a low-power management reset:

(1) Reset generated when entering Standby mode:

This type of reset is enabled by resetting nRST\_STDBY bit in User Option Bytes. In this case, whenever a Standby mode entry sequence is successfully executed, the device is reset instead of entering Standby mode.

(2) Reset when entering Stop mode:

This type of reset is enabled by resetting nRST\_STOP bit in User Option Bytes. In this case, whenever a Stop mode entry sequence is successfully executed, the device is reset instead of entering Stop mode.

#### 1.4.1.2 Power reset

A power reset is generated when one of the following events occurs:

- (1) Power-on/power-down reset (POR/PDR reset)

- (2) When exiting Standby mode

## 1.4.1.3 Backup domain reset

The backup domain has two specific resets that affect only the backup domain.

A backup domain reset is generated when one of the following events occurs:

(1) Software reset, triggered by setting the BDRST bit in the Backup domain control register (RCC\_BDCR).

(2) VDD or VBAT power on, if both supplies have previously been powered off.

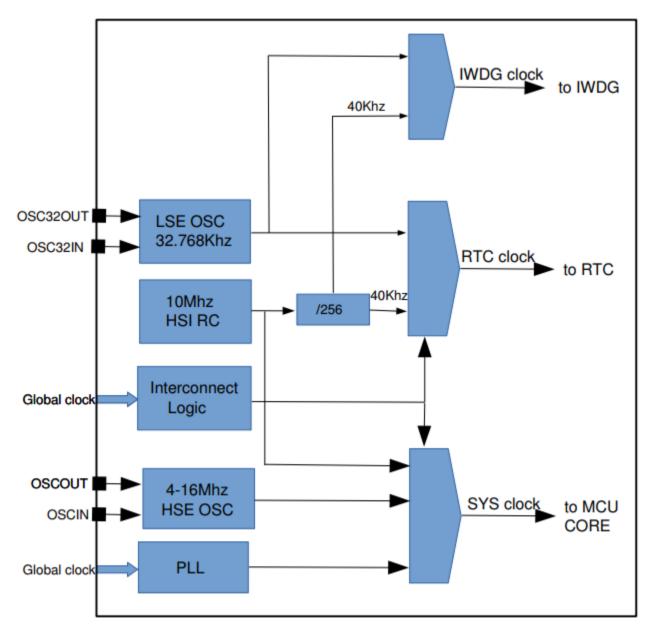

#### 1.4.2 Clocks

Three different clock sources can be used to drive the system clock (SYSCLK):

- (1) HSI oscillator clock

- (2) HSE oscillator clock

- (3) PLL clock

- 22 / 108

#### (4) FPGA global clocks

The devices have the following two secondary clock sources:

(1) 40 kHz low speed internal RC (LSI), which drives the independent watchdog and optionally the RTC used for Auto-wakeup from Stop/Standby mode.

(2) 32.768 kHz low speed external crystal (LSE crystal), which optionally drives the real-time clock (RTCCLK)

Each clock source can be switched on or off independently when it is not used, to optimize power consumption.

**Clock tree**

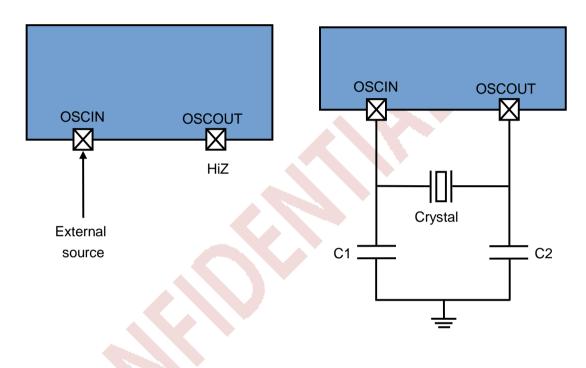

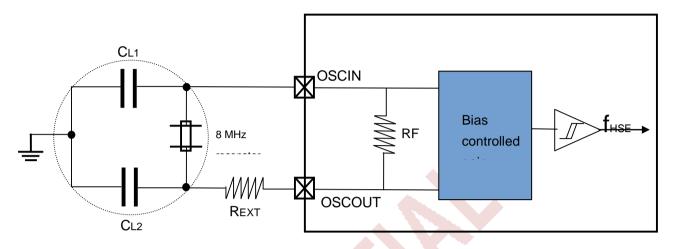

#### 1.4.2.1 HSE clock

The high speed external clock signal (HSE) can be generated from two possible clock sources:

(1) HSE external crystal/ceramic resonator

(2) HSE user external clock

The resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

#### External source (HSE bypass)

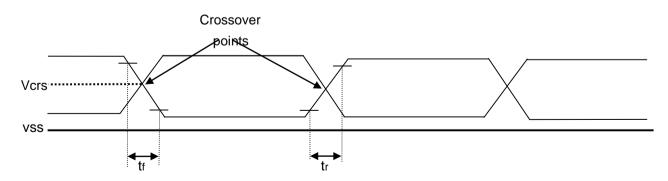

In this mode, an external clock source must be provided. It can have a frequency of up to 100 MHz. You select this mode by setting the HSEBYP and HSEON bits in the Clock control register (RCC\_CR). The external clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC\_IN pin while the OSC\_OUT pin should be left hi-Z.

#### External crystal/ceramic resonator (HSE crystal)

The 4 to 16 MHz external oscillator has the advantage of producing a very accurate rate on the main clock. Refer to the electrical characteristics section of the data sheet for more details. The HSERDY flag in the Clock control register (RCC\_CR) indicates if the high-speed external oscillator is stable or not. At startup, the clock is not released until this bit is set by hardware. An interrupt can be generated if enabled in the Clock interrupt register (RCC\_CIR). The HSE Crystal can be switched on and off using the HSEON bit in the Clock control register (RCC\_CR).

#### 1.4.2.2 HSI clock

The HSI clock signal is generated from an internal Oscillator and can be used directly as a system clock.

The HSI internal oscillator has the advantage of providing a clock source at low cost (no external components). It also has a faster startup time than the HSE crystal oscillator.

#### 1.4.2.3 PLL

The internal PLL can be used to multiply HSE crystal output clock frequency. An interrupt can be generated when the PLL is ready if enabled in the Clock interrupt register (RCC\_CIR). If the USB interface is used in the application, the PLL must be programmed to output 48 MHz. This is needed to provide a 48 MHz USBCLK.

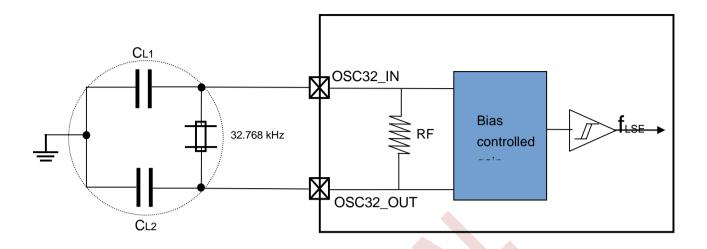

#### 1.4.2.4 LSE clock

The LSE crystal is a 32.768 kHz Low Speed External crystal or ceramic resonator. It has the advantage providing a low-power but highly accurate clock source to the real-time clock peripheral (RTC) for clock/calendar or other timing functions.

The LSE crystal is switched on and off using the LSEON bit in Backup domain control register (RCC\_BDCR).

The LSERDY flag in the Backup domain control register (RCC\_BDCR) indicates if the LSE crystal is stable or not. At startup, the LSE crystal output clock signal is not released until this bit is set by hardware. An interrupt can be generated if enabled in the Clock interrupt register (RCC\_CIR).

#### External source (LSE bypass)

In this mode, an external clock source must be provided. It can have a frequency of up to 1 MHz. You select this mode by setting the LSEBYP and LSEON bits in the Backup domain control register (RCC\_BDCR). The external clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC32\_IN pin while the OSC32\_OUT pin should be left Hi-Z.

#### 1.4.2.5 LSI clock

The LSI clock is HSI divided by 256. It can be kept running in Stop mode for the independent watchdog (IWDG) and Auto-wakeup unit (AWU). The clock frequency is around 40 kHz (between 30 kHz and 60 kHz).

## 1.4.2.6 System clock (SYSCLK) selection

After a system reset, the HSI oscillator is selected as system clock. When a clock source is used directly or through the PLL as system clock, it is not possible to stop it.

A switch from one clock source to another occurs only if the target clock source is ready (clock stable after startup delay or PLL locked). If a clock source which is not yet ready is selected, the switch will occur when the clock source will be ready. Status bits in the Clock control register (RCC\_CR) indicate which clock(s) is (are) ready and which clock is currently used as system clock.

#### 1.4.2.7 RTC clock

The RTCCLK clock source can be either the CLKLOCAL(from fpga core logic), LSE or LSI clocks. This is selected by programming the RTCSEL[1:0] bits in the Backup domain control register (RCC\_BDCR).

This selection cannot be modified without resetting the Backup domain.

The LSE clock is in the Backup domain, whereas the HSE and LSI clocks are not.

Consequently:

(1) If LSE is selected as RTC clock:

The RTC continues to work even if the VDD supply is switched off, provided the VBAT supply is maintained.

(2) If LSI is selected as Auto-Wakeup unit (AWU) clock:

The AWU state is not guaranteed if the VDD supply is powered off.

(3) If the CLKLOCAL is used as the RTC clock:

The RTC state is not guaranteed if the VDD supply is powered off or if the internal voltage regulator is powered off (removing power from the 1.2 V domain).

The DPB bit (disable backup domain write protection) in the Power controller register must be set to 1.

#### 1.4.2.8 Watchdog clock

If the Independent watchdog (IWDG) is started by either hardware option or software access,

(1) Under run or stop mode

Select LSE or LSI clock source by setting the IWDG\_STOP\_CLKSEL bit in the Backup domain control register (\*\*\*\*\*).

(2) Under Standby mode

HW will select LSE as clock source for IWDG.

## 1.4.3 Reset and clock control registers

#### 1.4.3.1 Clock control register (RCC\_CR)

Address offset:

Reset value:

| 31      | 30 | 29 | 28 | 27 | 26 | 25  | 24  | 23       | 22 | 21 | 20 | 19 | 18  | 17  | 16  |

|---------|----|----|----|----|----|-----|-----|----------|----|----|----|----|-----|-----|-----|

|         |    |    |    |    |    | PLL | PLL |          |    |    |    |    | HSE | HSE | HSE |

| reserve | d  |    |    |    |    | RDY | ON  | reserved |    |    |    |    | BYP | RDY | ON  |

|         |    |    |    |    |    | r   | rw  |          |    |    |    |    | rw  | r   | rw  |

| i.      | I  |    |    | 1  |    |     | 1   |          |    |    |    |    |     | i.  |     |

| 15      | 14 | 13 | 12 | 11 | 10 | 9   | 8   | 7        | 6  | 5  | 4  | 3  | 2   | 1   | 0   |

| reserve | d  |    |    |    |    |     |     |          |    |    |    |    |     |     |     |

Bit 25 PLLRDY: PLL clock ready flag

Set by hardware to indicate that the PLL is locked.

0: PLL unlocked

1: PLL locked

Bit 24 PLLON: PLL enable

Set and cleared by software to enable PLL.

Cleared by hardware when entering Stop or Standby mode. This bit can not be reset if the PLL clock is used as system clock or is selected to become the system clock.

0: PLL OFF

1: PLL ON

Bit 18 HSEBYP: External high-speed clock bypass

Set and cleared by software to bypass the oscillator with an external clock. The external clock must be enabled with the HSEON bit set, to be used by the device. The HSEBYP bit can be written only if the HSE oscillator is disabled.

0: external 4-16 MHz oscillator not bypassed

1: external 4-16 MHz oscillator bypassed with external clock

Bit 17 HSERDY: External high-speed clock ready flag. Set by hardware to indicate that the HSE oscillator is stable. This bit needs 6 cycles of the HSE oscillator clock to fall down after HSEON reset.

0: HSE oscillator not ready

1: HSE oscillator ready

Bit 16 HSEON: HSE clock enable

Set and cleared by software. Cleared by hardware to stop the HSE oscillator when entering Stop

or Standby mode. This bit cannot be reset if the HSE oscillator is used directly or indirectly as the system clock.

0: HSE oscillator OFF

1: HSE oscillator ON

| 1.4.3.2 | Clock configuration register (RCC_CFGR) |

|---------|-----------------------------------------|

|---------|-----------------------------------------|

- 1.4.3.3 Clock interrupt register (RCC\_CIR)

- **1.4.3.4** APB2 peripheral reset register (RCC\_APB2RSTR)

- 1.4.3.5 APB1 peripheral reset register (RCC\_APB1RSTR)

- **1.4.3.6** AHB peripheral clock enable register (RCC\_AHBENR)

- 1.4.3.7 APB2 peripheral clock enable register (RCC\_APB2ENR)

- 1.4.3.8 APB1 peripheral clock enable register (RCC\_APB1ENR)

#### **1.4.3.9** Backup domain control register (RCC\_BDCR)

Address offset:

Reset value: 0x0000 0000, reset by Backup domain Reset.

The LSEON, LSEBYP, RTCSEL and RTCEN bits of the Backup domain control register (RCC\_BDCR) are in the Backup domain. As a result, after Reset, these bits are write-protected and the DBP bit in the Power control register (PWR\_CR) has to be set before these can be modified.

These bits are only reset after a Backup domain Reset. Any internal or external Reset will not have any effect on these bits.

| 31        | 30       | 29 | 28 | 27 | 26 | 25     | 24     | 23       | 22 | 21 | 20 | 19  | 18  | 17  | 16    |

|-----------|----------|----|----|----|----|--------|--------|----------|----|----|----|-----|-----|-----|-------|

| reserved  | 1        |    |    |    |    |        |        |          |    |    |    |     |     |     | BDRST |

| ieser vee | 1        |    |    |    |    |        |        |          |    |    |    |     |     |     | rw    |

| 1         | 1        |    |    |    |    |        |        | I        |    |    |    | 1 1 |     |     | 1     |

| 15        | 14       | 13 | 12 | 11 | 10 | 9      | 8      | 7        | 6  | 5  | 4  | 3   | 2   | 1   | 0     |

| RTC       |          |    |    |    |    | RTCSEI | [1:0]  |          |    |    |    |     | LSE | LSE | LSEON |

| EN        | reserved | l  |    |    |    | KICSEI | 2[1.0] | reserved |    |    |    |     | BYP | RDY | LSEON |

| rw        |          |    |    |    |    | rw     | rw     |          |    |    |    |     | rw  | r   | rw    |

Bit 16 BDRST: Backup domain software reset

- Set and cleared by software.

- 0: Reset not activated

- 1: Resets the entire Backup domain

Bit 15 RTCEN: RTC clock enable

Set and cleared by software.

- 0: RTC clock disabled

- 1: RTC clock enabled

- Bits 9:8 RTCSEL[1:0]: RTC clock source selection

Set by software to select the clock source for the RTC. Once the RTC clock source has been selected, it cannot be changed anymore unless the Backup domain is reset. The BDRST bit can be used to reset them.

- 00: No clock

- 01: LSE oscillator clock used as RTC clock

- 10: LSI oscillator clock used as RTC clock

- 11: Local clock used as RTC clock

Bit 2 LSEBYP: External low-speed oscillator bypass

Set and cleared by software to bypass oscillator in debug mode. This bit can be written only when the external 32 kHz oscillator is disabled.

- 0: LSE oscillator not bypassed

- 1: LSE oscillator bypassed

Bit 1 LSERDY: External low-speed oscillator ready

Set and cleared by hardware to indicate when the external 32 kHz oscillator is stable. After the LSEON bit is cleared, LSERDY goes low after 6 external low-speed oscillator clock cycles.

- 0: External 32 kHz oscillator not ready

- 1: External 32 kHz oscillator ready

Bit 0 LSEON: External low-speed oscillator enable

Set and cleared by software.

- 0: External 32 kHz oscillator OFF

- 1: External 32 kHz oscillator ON

#### 1.4.3.10 Control/status register (RCC\_CSR)

Address: \*\*\*\*

Reset value: 0x0C00 0000, reset by system Reset, except reset flags by power Reset only.

| 15           | 14           | 13           | 12          | 11          | 10          | 9    | 8        | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------|--------------|--------------|-------------|-------------|-------------|------|----------|---|---|---|---|---|---|---|---|

| reserve<br>d | WWDG<br>RSTF | IWDG<br>RSTF | SFT<br>RSTF | POR<br>RSTF | PIN<br>RSTF | RMVF | reserved |   |   |   |   |   |   |   |   |

|              | rw           | rw           | rw          | rw          | rw          | rw   |          |   |   |   |   |   |   |   |   |

Bit 14 WWDGRSTF: Window watchdog reset flag Set by hardware when a window watchdog reset occurs. Cleared by writing to the RMVF bit.

0: No window watchdog reset occurred

1: Window watchdog reset occurred

Bit 13 IWDGRSTF: Independent watchdog reset flag

Set by hardware when an independent watchdog reset from VDD domain occurs.

Cleared by writing to the RMVF bit.

0: No watchdog reset occurred

1: Watchdog reset occurred

Bit 12 SFTRSTF: Software reset flag

Set by hardware when a software reset occurs.

Cleared by writing to the RMVF bit.

0: No software reset occurred

1: Software reset occurred

Bit 11 PORRSTF: POR/PDR reset flag Set by hardware when a POR/PDR reset occurs. Cleared by writing to the RMVF bit. 0: No POR/PDR reset occurred 1: POR/PDR reset occurred

Bit 10 PINRSTF: PIN reset flagSet by hardware when a reset from the NRST pin occurs.Cleared by writing to the RMVF bit.0: No reset from NRST pin occurred1: Reset from NRST pin occurred

Bit 8 RMVF: Remove reset flag

Set by software to clear the reset flags. 0: No effect 1: Clear the reset flags

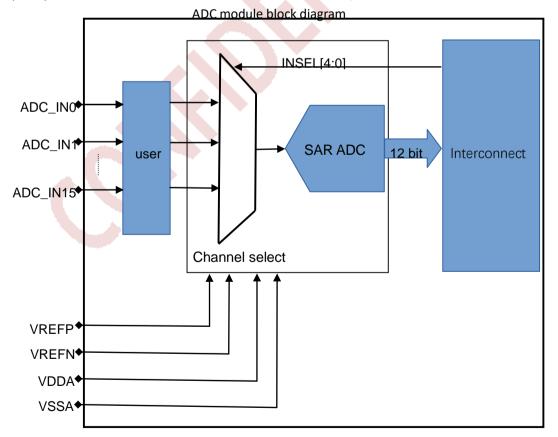

## 1.5 Analog-to-digital converter (ADC)

## 1.5.1 ADC introduction

The 12-bit ADC is a successive approximation analog-to-digital converter. It has up to 17 multiplexed channels allowing it measure signals from sixteen external and one internal sources. A/D conversion of the various channels can be performed in single, continuous, scan or discontinuous mode.

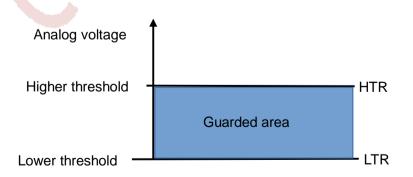

The analog watchdog feature allows the application to detect if the input voltage goes outside the user-defined high or low thresholds.

The ADC input clock is generated from the interconnect logic clock and it must not exceed 13 MHz.

## 1.5.2 Characteristics

(1) ADC sampling rate: 1 MSPS for 12-bit resolution

(2) Programmable sampling time

(3) DMA support

(4) 16 external analog inputs and 1 channel for internal temperature sensor (VSENSE) or for VBAT

(5) Converts a single channel or scans a sequence of channels

(6) Single mode converts selected inputs once per trigger

(7) Continuous mode converts selected inputs continuously

(8) Discontinuous mode

(9) SYNC mode(the device with two or more ADCs)

(10) Analog watchdog

(11) Interrupt generation: at the end of regular and inserted group conversions or analog watchdog event

(12) ADC supply requirements: 3.0V to 3.6V, and typical power supply voltage is 3.3V

(13) ADC input range: VREFN ≤VIN ≤VREFP

## **1.5.3** Pins and internal signals

Table 4-1. ADC internal signals

#### AG32 MCU

| Internal signal name | Signal type | Description                                |

|----------------------|-------------|--------------------------------------------|

| Vtemp-sense          | input       | Internal temperature sensor output voltage |

| Vbat                 | input       | Vbat pin voltage                           |

#### Table 4-2. ADC pins definition

| Signal type                         | Remarks                                                                                                        |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Input, analog power supply          | Analog power supply equal to VDD and $3.0 \text{ V} \leq \text{VDDA} \leq 3.6 \text{ V}$                       |

| Input, analog power ground          | Ground for analog power supply equal to VSS                                                                    |

| Input, analog reference positive    | The positive reference voltage for the ADC, $3.0 \text{ V} \leq \text{VREFP} \leq \text{VDDA}$                 |

| Input, analog<br>reference negative | The negative reference voltage for the ADC, VREFN = VSSA                                                       |

| Input, Analog signals               | Up to 16 external channels                                                                                     |

|                                     | Input, analog power<br>supplyInput, analog power<br>groundInput, analog<br>reference positiveInput, analog<br> |

The ADCCLK clock provided by global clock from interconnect core logic. The maximum frequency is 14MHz.

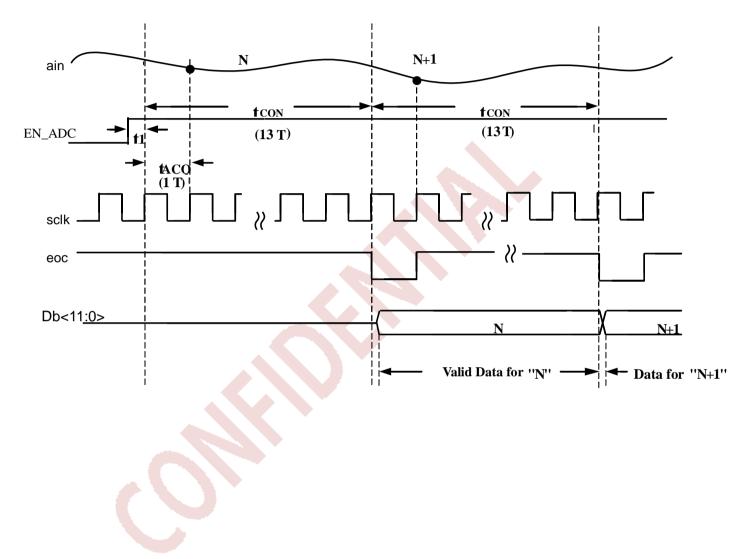

## 1.5.4 Timing diagram

After the start of ADC conversion and after 13 clock cycles, the EOC flag is set and the 12-bit Data is ready.

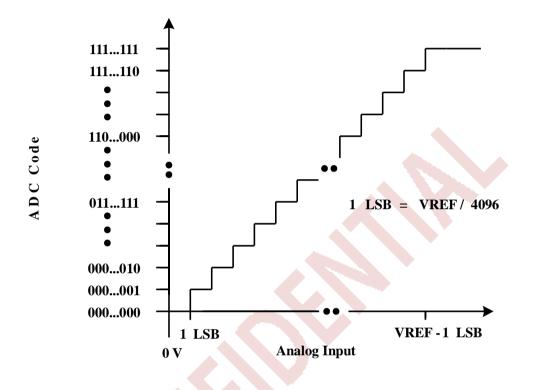

### 1.5.5 ADC output data

The output coding is straight binary. The designed code transitions occur at successive integer LSB values; that is, 1LSB, 2LSB, and so on. The LSB size is VREF/4096.

## 1.5.6 Analog watchdog

The AWD analog watchdog status bit is set if the analog voltage converted by the ADC is below a low threshold or above a high threshold.

#### **1.5.7** Temperature sensor

The temperature sensor can be used to measure the ambient temperature of the device. The sensor output voltage can be converted into a digital value by ADC. The sampling time for the temperature sensor is recommended to be set to at least 20µs.

The output voltage of the temperature sensor changes linearly with temperature. Because there is an offset, which is up to 45°C and varies from chip to chip due to process variation, the internal temperature sensor is more suited for applications that detect temperature variations instead of absolute temperature.

## **1.6 Digital-to-analog converter (DAC)**

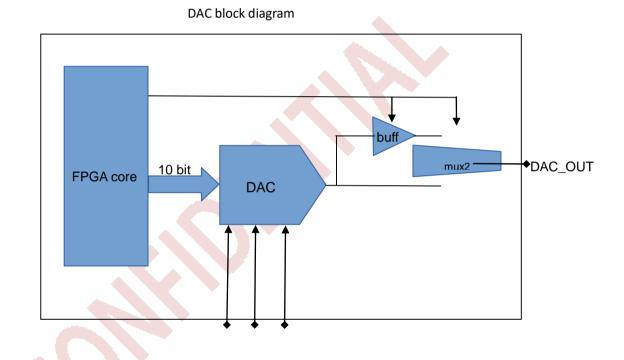

#### 1.6.1 Overview

The Digital-to-analog converter converts 10-bit digital data to a voltage on the external pins. DMA can be used to update the digital data on external triggers. The output voltage can be optionally buffered for higher drive capability. The two DACs can work independently or concurrently.

## **1.6.2** DAC main features

- (1) Two DAC converters: one output channel each

- (2) Conversion triggered by external triggers

- (3) Dual DAC channel independent or simultaneous conversions

- (4) Configurable internal buffer

- (5) DMA capability for each channel

- (6) External triggers for conversion

- (7) Input voltage reference VREFP

| Name     | Signal type                         | Remarks                                                                                      |

|----------|-------------------------------------|----------------------------------------------------------------------------------------------|

| VDDA     | Input, analog power supply          | Analog power supply equal to VDD and $3.0 \text{ V} \le \text{VDDA} \le 3.6 \text{ V}$       |

| VSSA     | Input, analog power ground          | Ground for analog power supply equal to VSS                                                  |

| VREP     | Input, analog<br>reference positive | The positive reference voltage for the ADC, $3.0 \text{ V} \le \text{VREFP} \le \text{VDDA}$ |

| DAC_OUTx | DACx analog output                  | Analog output signal                                                                         |

## **1.6.3 DAC output buffer enable**

The DAC integrates two output buffers that can be used to reduce the output impedance, and to drive external loads directly without having to add an external operational amplifier.

## 1.6.4 DAC output voltage

The analog output voltage on the DAC pin is determined by the following equation: DACoutput = VREFP \* DAC\_Dout/1024 The digital input is linearly converted to an analog output voltage, its range is 0 to VREFP.

## 1.7 Comparator (CMP)

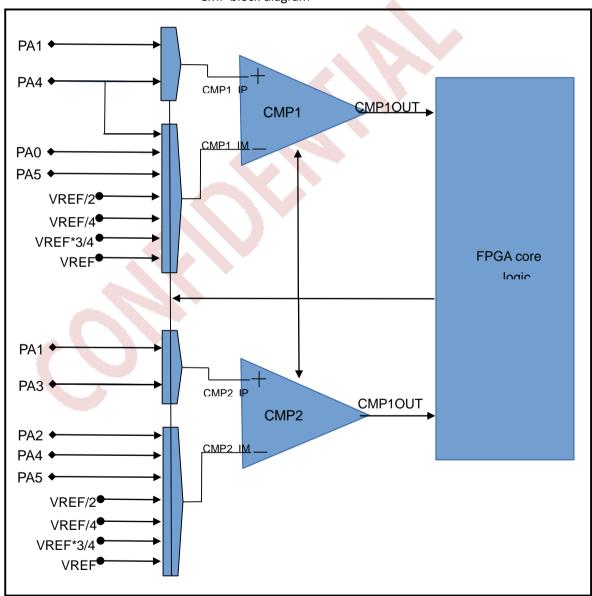

## 1.7.1 Overview

The general purpose comparators, CMP0 and CMP1, can work either standalone or together with the timers.

It could be used to wake up the MCU from low-power mode by an analog signal, provide a trigger source when an analog signal is in a certain condition, achieves some current control by working together with a PWM output of a timer and the DAC.

## 1.7.2 Characteristic

- (1) Rail-to-rail comparators

- (2) Configurable hysteresis

- (3) Configurable speed and consumption

- (4) Each comparator has configurable analog input source

- (5) The whole or sub-multiple values of internal reference voltage Window comparator

- (6) Outputs to I/O

- (7) Outputs to timers for triggering

## 1.8 Real-time clock (RTC)

## **1.8.1 RTC introduction**

The real-time clock is an independent timer. The RTC provides a set of continuously running counters which can be used, with suitable software, to provide a clock-calendar function. The counter values can be written to set the current time/date of the system.

The RTC core and clock configuration (RCC\_BDCR register) are in the Backup domain, which means that RTC setting and time are kept after reset or wakeup from Standby mode. After reset, access to the Backup registers and RTC is disabled and the Backup domain (BKP) is protected against possible parasitic write access. To enable access to the Backup registers and the RTC, proceed as follows:

(1) Enable the power and backup interface clocks by setting the PWREN and BKPEN bits in the RCC\_APB1ENR register

(2) Set the DBP bit the Power Control Register (PWR\_CR) to enable access to the Backup registers and RTC.

## 1.8.2 RTC main features

- Programmable pre-scaler : division factor up to 2^20

- 32-bit programmable counter for long-term measurement

- The RTC clock source could be any of the following ones:

- (1) CLKLOCAL from fpga core logic

- (2) LSE oscillator clock

- (3) LSI oscillator clock

- Two separate reset types:

- (1) The APB1 interface is reset by system reset

- (2) The RTC Core (Pre-scaler, Alarm, Counter and Divider) is reset only by a Backup domain reset.

- Three dedicate interrupt lines:

- (1) Alarm interrupt, for generating a software programmable alarm interrupt.

(2) Seconds interrupt, for generating a periodic interrupt signal with a programmable period length (up to 1 second).

(3) Overflow interrupt, to detect when the internal programmable counter rolls over to zero.

## 1.8.3 RTC functional description

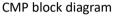

The RTC consists of two main units. The first one (APB1 Interface) is used to interface with the APB1 bus. This unit also contains a set of 16-bit registers accessible from the APB1 bus in read or write mode. The APB1 interface is clocked by the APB1 bus clock in order to interface with the APB1 bus.

The other unit (RTC Core) consists of a chain of programmable counters made of two main blocks. The first block is the RTC pre-scaler block, which generates the RTC time base TR\_CLK that can be programmed to have a period of up to 1 second. It includes a 20-bit programmable divider (RTC Pre-scaler). Every TR\_CLK period, the RTC generates an interrupt (Second Interrupt) if it is enabled in the RTC\_CR register. The second block is a 32-bit programmable counter that can be initialized to the current system time. The system time is incremented at the TR\_CLK rate and compared with a programmable date (stored in the RTC\_ALR register) in order to generate an alarm interrupt, if enabled in the RTC\_CR control register.

RTC simplified block diagram

### **Resetting RTC registers**

All system registers are asynchronously reset by a System Reset or Power Reset, except for RTC\_PRL, RTC\_ALR, RTC\_CNT, and RTC\_DIV.

The RTC\_PRL, RTC\_ALR, RTC\_CNT, and RTC\_DIV registers are reset only by a Backup Domain reset.

### **Reading RTC registers**

The RTC core is completely independent from the RTC APB1 interface.

Software accesses the RTC pre-scaler, counter and alarm values through the APB1 interface but the associated readable registers are internally updated at each rising edge of the RTC clock resynchronized by the RTC APB1 clock. This is also true for the RTC flags.

This means that the first read to the RTC APB1 registers may be corrupted (generally read as 0) if the APB1 interface has previously been disabled and the read occurs immediately after the APB1 interface is enabled but before the first internal update of the registers. This can occur if:

(1) A system reset or power reset has occurred

(2) The MCU has just woken up from Standby mode

(3) The MCU has just woken up from Stop mode

In all the above cases, the RTC core has been kept running while the APB1 interface was disabled (reset, not clocked or unpowered).

Consequently when reading the RTC registers, after having disabled the RTC APB1 interface, the software must first wait for the RSF bit (Register Synchronized Flag) in the RTC\_CRL register to be set by hardware.

Note that the RTC APB1 interface is not affected by WFI and WFE low-power modes.

### **Configuring RTC registers**

To write in the RTC\_PRL, RTC\_CNT, RTC\_ALR registers, the peripheral must enter Configuration Mode. This is done by setting the CNF bit in the RTC\_CRL register.

In addition, writing to any RTC register is only enabled if the previous write operation is finished. To enable the software to detect this situation, the RTOFF status bit is provided in the RTC\_CR register to indicate that an update of the registers is in progress. A new value can be written to the RTC registers only when the RTOFF status bit value is '1'.

Configuration procedure

1. Poll RTOFF, wait until its value goes to '1'

- 2. Set the CNF bit to enter configuration mode

- 3. Write to one or more RTC registers

- 4. Clear the CNF bit to exit configuration mode

5. Poll RTOFF, wait until its value goes to '1' to check the end of the write operation.

The write operation only executes when the CNF bit is cleared; it takes at least three RTCCLK cycles to complete.

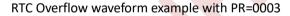

### **RTC flag assertion**

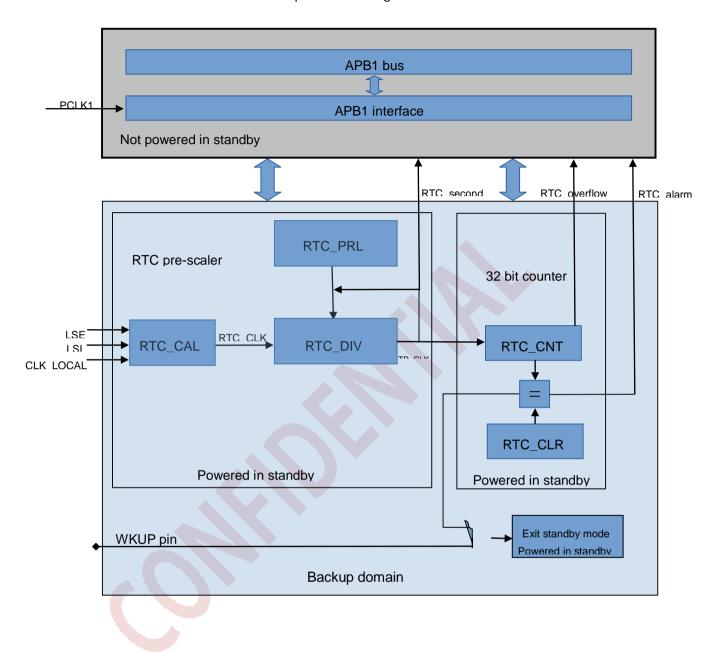

The RTC Second flag (SECF) is asserted on each RTC Core clock cycle before the update of the RTC Counter.

The RTC Overflow flag (OWF) is asserted on the last RTC Core clock cycle before the counter reaches 0x0000.

The RTC\_Alarm and RTC Alarm flag (ALRF) are asserted on the last RTC Core clock cycle before the counter reaches the RTC Alarm value stored in the Alarm register increased by one (RTC\_ALR + 1). The write operation in the RTC Alarm and RTC Second flag must be synchronized by using one of the following sequences:

(1) Use the RTC Alarm interrupt and inside the RTC interrupt routine, the RTC Alarm and/or RTC Counter registers are updated.

(2) Wait for SECF bit to be set in the RTC Control register. Update the RTC Alarm and/or the RTC Counter register.

RTC second and alarm waveform example with PR=0003, ALARM=00004

## **1.8.4 RTC registers**

### RTC control register high (RTC\_CRH)

Address offset: 0x00 Reset value: 0x0000

| 15      | 14      | 13       | 12        | 11      | 10    | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2    | 1     | 0     |

|---------|---------|----------|-----------|---------|-------|---|---|---|---|---|---|---|------|-------|-------|

| reserve | d       |          |           |         |       |   |   |   |   |   |   |   | OWIE | ALRIE | SECIE |

| leserve | u       |          |           |         |       |   |   |   |   |   |   |   | rw   | rw    | rw    |

| Bi+ 2 C | )\\/IE· | Ovorflo  | w inter   | runt or | aablo |   |   |   |   |   |   |   |      |       |       |

|         |         |          | pt is ma  |         | lable |   |   |   |   |   |   |   |      |       |       |

|         |         |          | pt is ena |         |       |   |   |   |   |   |   |   |      |       |       |

|         |         |          |           |         |       |   |   |   |   |   |   |   |      |       |       |

| Bit 1 A | ALRIE:  | Alarm i  | nterrup   | t enab  | le    |   |   |   |   |   |   |   |      |       |       |

| 0: Alaı | rm inte | errupt i | s maske   | ed.     |       |   |   |   |   |   |   |   |      |       |       |

| 1: Alaı | rm inte | errupt i | s enable  | ed.     |       |   |   |   |   |   |   |   |      |       |       |

Bit 0 SECIE: Second interrupt enable

- 0: Second interrupt is masked.

- 1: Second interrupt is enabled.

### RTC control register low (RTC\_CRL)

Address offset: 0x04 Reset value: 0x0020

| 1 1      | -  |    |    |    |    |   | 1 |   |   |       |     |       | i     | I.    | 1     | i i |

|----------|----|----|----|----|----|---|---|---|---|-------|-----|-------|-------|-------|-------|-----|

| 15       | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5     | 4   | 3     | 2     | 1     | 0     |     |

|          |    |    |    |    |    |   |   |   |   | RTOFF | CNF | RSF   | OWF   | ALRF  | SECF  |     |

| reserved |    |    |    |    |    |   |   |   |   | r     | rw  | rc_w0 | rc_w0 | rc_w0 | rc_w0 |     |

### Bit 5 RTOFF: RTC operation OFF

With this bit the RTC reports the status of the last write operation performed on its registers, indicating if it has been completed or not. If its value is '0' then it is not possible to write to any of the RTC registers. This bit is read only.

0: Last write operation on RTC registers is still ongoing.

1: Last write operation on RTC registers terminated.

### Bit 4 CNF: Configuration flag

This bit must be set by software to enter in configuration mode so as to allow new values to be written in the RTC\_CNT, RTC\_ALR or RTC\_PRL registers. The write operation is only executed

when the CNF bit is reset by software after has been set.

0: Exit configuration mode (start update of RTC registers).

1: Enter configuration mode.

#### Bit 3 RSF: Registers synchronized flag

This bit is set by hardware at each time the RTC\_CNT and RTC\_DIV registers are updated and cleared by software. Before any read operation after an APB1 reset or an APB1 clock stop, this bit must be cleared by software, and the user application must wait until it is set to be sure that the RTC\_CNT, RTC\_ALR or RTC\_PRL registers are synchronized.

0: Registers not yet synchronized.

1: Registers synchronized.

#### Bit 2 OWF: Overflow flag

This bit is set by hardware when the 32-bit programmable counter overflows. An interrupt is generated if OWIE=1 in the RTC\_CRH register. It can be cleared only by software. Writing '1' has no effect.

0: Overflow not detected

1: 32-bit programmable counter overflow occurred.

#### Bit 1 ALRF: Alarm flag

This bit is set by hardware when the 32-bit programmable counter reaches the threshold set in the RTC\_ALR register. An interrupt is generated if ALRIE=1 in the RTC\_CRH register. It can be cleared only by software. Writing '1' has no effect.

0: Alarm not detected

1: Alarm detected

#### Bit 0 SECF: Second flag

This bit is set by hardware when the 32-bit programmable pre-scaler overflows, thus incrementing the RTC counter. Hence this flag provides a periodic signal with a period corresponding to the resolution programmed for the RTC counter (usually one second). An interrupt is generated if SECIE=1 in the RTC\_CRH register. It can be cleared only by software. Writing '1' has no effect.

0: Second flag condition not met.

1: Second flag condition met.

### RTC pre-scaler load register (RTC\_PRLH / RTC\_PRLL)

The Pre-scaler Load registers keep the period counting value of the RTC pre-scaler. They are write-protected by the RTOFF bit in the RTC\_CR register, and a write operation is allowed if the RTOFF value is '1'.

### RTC pre-scaler load register high (RTC\_PRLH)

Address offset: 0x08 Write only (see Section 18.3.4: Configuring RTC registers) Reset value: 0x0000

| 15        | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3       | 2   | 1 | 0 |

|-----------|----|----|----|----|----|---|---|---|---|---|---|---------|-----|---|---|

| racorruad | 1  |    |    |    |    |   |   |   |   |   |   | PRL[19: | 16] |   |   |

| reserved  | 1  |    |    |    |    |   |   |   |   |   |   | w       | w   | w | w |

Bits 3:0 PRL[19:16]: RTC pre-scaler reload value high

These bits are used to define the counter clock frequency according to the following formula:  $f_TR_CLK = f_RTCCLK/(PRL[19:0]+1)$

## RTC pre-scaler load register low (RTC\_PRLL)

Address offset: 0x0C Write only Reset value: 0x8000

| 15      | 14  | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|-----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| PRL[15: | :0] |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| w       | w   | w  | w  | w  | w  | w | w | W | w | w | w | w | w | w | w |

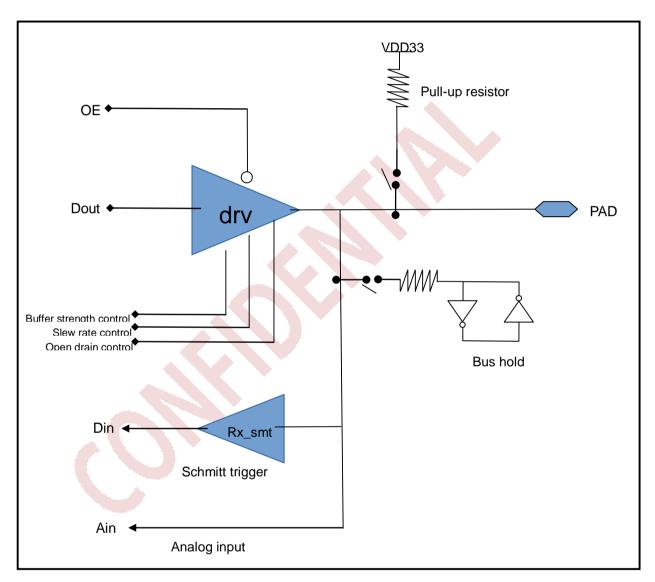

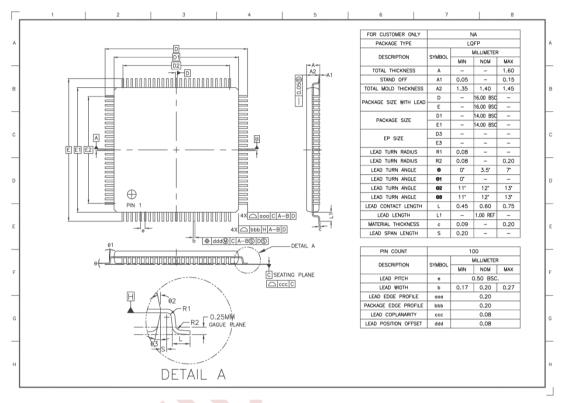

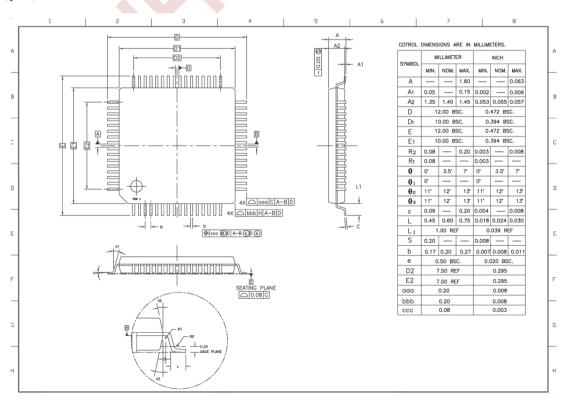

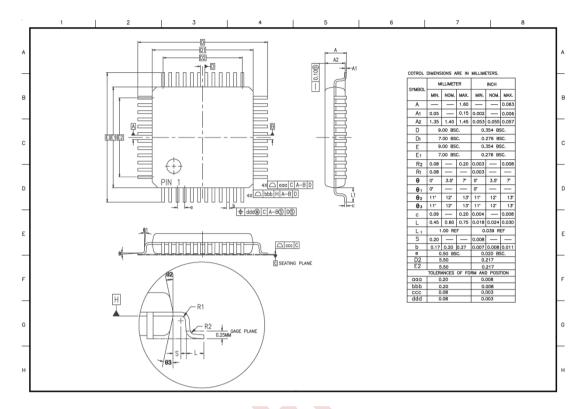

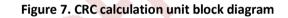

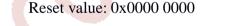

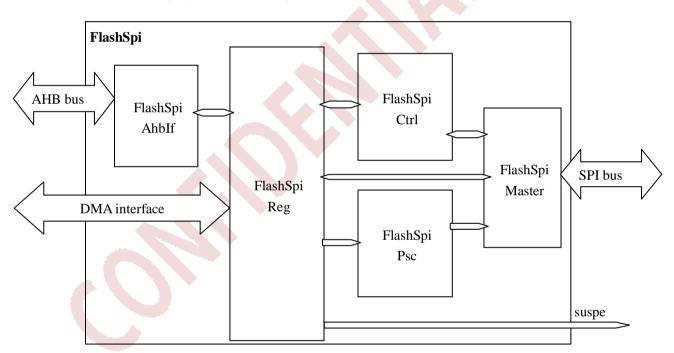

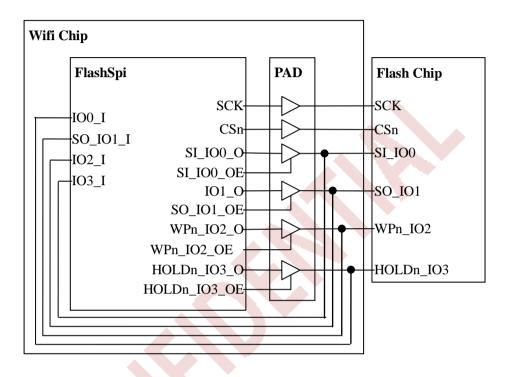

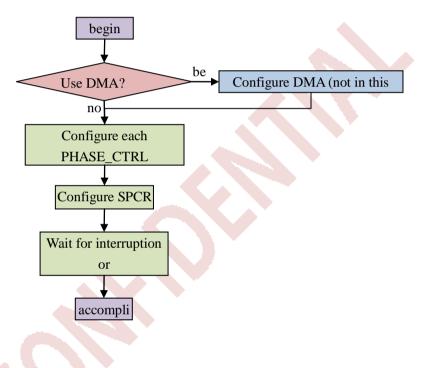

Bits 15:0 PRL[15:0]: RTC pre-scaler reload value low